IBM Z: Accessing the LPAR Resource Assignment Task

Washington Systems Center

This document can be found on the web, <a href="www.ibm.com/support/techdocs">www.ibm.com/support/techdocs</a>

Document ID: WP102754

Version Date: May 11, 2018

If you have any comments or feedback on the contents of this document, please send an e-mail to:

Ryan McCarry (ryan.mccarry@ibm.com)

The original document was written by:

Ryan McCarry (ryan.mccarry@ibm.com)

Thank you to the reviewer:

John Burg (jpburg@us.ibm.com)

The new View Partition Resource Assignments task will be available on the HMC and SE. It is a display only task. On the SE, this task can be used in PEDEBUG, SYSPROG and SERVICE modes. On the HMC, this task can be used in PEDEBUG and SERVICE modes.

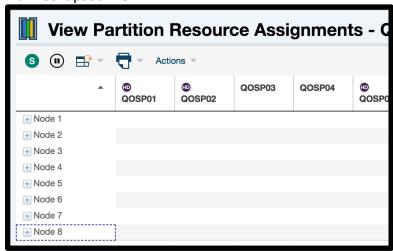

The View Partition Resource Assignments task targets the CPC and provides a snapshot of all active partitions and associated processor information. The information displayed for each partition includes the HiperDispatch setting and processor information (number, CPU type and polarity) displayed within the Node and Chip locations.

## Steps:

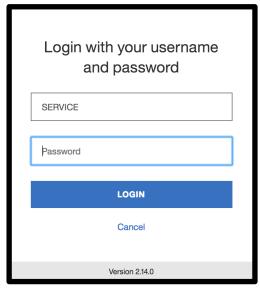

1. Log on to the HMC as PEDEBUG or SERVICE modes.

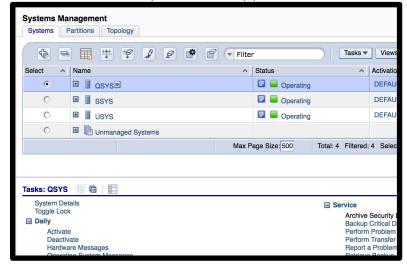

- 2. Select the System Management view

- 3. Place a check next to your z14 family processor

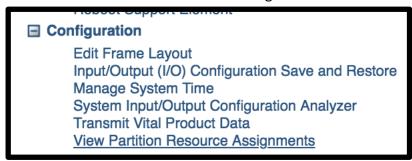

4. Find the task View Partition Resource Assignments under the Configurations task list

- 5. Partitions can be expanded or collapsed to show relevant LPAR information

- a. Collapsed View

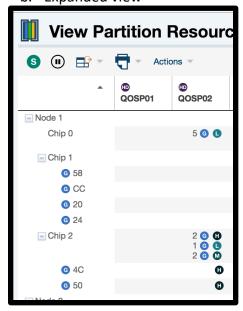

b. Expanded view

## Sample Output/Key

|           | (ID)<br>QOSP01 | D<br>QOSP02             | QOSP03 | QOSP04 | (ID)<br>QOSP05 | QOSP06 | D<br>QOSP07 | D<br>QOSP09             | (ID)<br>QOSP0F | QOSP160      |

|-----------|----------------|-------------------------|--------|--------|----------------|--------|-------------|-------------------------|----------------|--------------|

| Node<br>1 |                |                         |        |        |                |        |             |                         |                |              |

| Chip<br>0 |                | 2 🕝 🕒                   |        |        |                |        |             | 3 🕝 🕒                   |                |              |

| Chip      |                | 2 G H<br>4 G L<br>2 G M |        |        |                |        |             |                         |                |              |

| Chip<br>2 |                |                         |        |        |                |        |             |                         |                |              |

| Node<br>2 |                |                         |        |        |                |        |             |                         |                |              |

| Chip<br>0 |                |                         |        | 2 🕝 斜  |                |        |             | 2 G H<br>3 G L<br>2 G M |                |              |

| Chip<br>1 |                |                         |        |        |                |        |             | 6 <b>G L</b>            |                |              |

| Node<br>3 |                |                         |        |        |                |        |             |                         |                |              |

| Chip<br>0 |                |                         |        |        |                |        |             |                         | 2 🕝 D          | 5 <b>G D</b> |

| Chip<br>1 |                |                         |        |        |                |        |             |                         |                | 8 🕝 📵        |